Vi điều khiển AVR Atmel ATmega2564 8bit

Đặc trưng

- Hỗ trợ mạng bằng cách lọc nhiều địa chỉ PAN được hỗ trợ bằng phần cứng

- Phần cứng nâng cao hỗ trợ giảm mức tiêu thụ điện năng

- Bộ vi điều khiển 8-bit AVR® hiệu suất cao, công suất thấp

- Kiến trúc RISC nâng cao

- 135 hướng dẫn mạnh mẽ - Thực hiện hầu hết các chu kỳ đồng hồ duy nhất

- Thanh ghi làm việc cho mục đích chung 32 × 8 / Hệ số nhân 2 chu kỳ trên chip

- Thông lượng lên đến 16 MIPS ở 16 MHz và 1.8V – Hoạt động hoàn toàn tĩnh

- Bộ nhớ dữ liệu và chương trình không thay đổi

- 256K/128K/64K Byte Flash Tự Lập Trình Trong Hệ Thống

- Độ bền: 10'000 Chu kỳ Ghi/Xóa ở 125°C (25'000 Chu kỳ ở 85°C)

- EEPROM 8K/4K/2K Byte

- Độ bền: 20'000 Chu kỳ Ghi/Xóa ở 125°C (100'000 Chu kỳ ở 25°C)

- SRAM nội bộ 32K/16K/8K Byte

- JTAG (Tương thích với chuẩn IEEE 1149.1) Giao diện

- Khả năng quét ranh giới theo JTAG Tiêu chuẩn

- Hỗ trợ gỡ lỗi trên chip mở rộng

- Lập trình Flash EEPROM, Cầu chì và Bit khóa thông qua JTAG giao diện

- Tính năng ngoại vi

- Nhiều kênh Timer/Counter & PWM

- Bộ đếm thời gian thực với bộ dao động riêng biệt

- Bộ chuyển đổi A/D 10-bit, 330 ks/s; Bộ so sánh tương tự; Cảm biến nhiệt độ trên chip

- Giao diện nối tiếp SPI Master/Slave

- Hai USART nối tiếp có thể lập trình

- Giao diện nối tiếp 2 dây định hướng byte

- Trình xử lý ngắt nâng cao và chế độ tiết kiệm điện

- Bộ đếm thời gian giám sát với bộ dao động riêng biệt trên chip

- Thiết lập lại khi bật nguồn và Bộ phát hiện hiện tượng mất điện ở mức thấp

- Bộ thu phát công suất thấp tích hợp hoàn toàn cho băng tần ISM 2.4 GHz

- Công suất cao Amphỗ trợ lifier bằng cách triệt tiêu thùy bên phổ TX

- Tốc độ dữ liệu được hỗ trợ: 250 kb/giây và 500 kb/giây, 1 Mb/giây, 2 Mb/giây

- -100 dBm Độ nhạy RX; Công suất đầu ra TX lên tới 3.5 dBm

- MAC được hỗ trợ phần cứng (Tự động xác nhận, Tự động thử lại)

- Bộ đếm ký hiệu IEEE 32 802.15.4 bit

- SFD-Phát hiện, Lan truyền; Giảm Lan truyền; Đóng khung; Tính toán CRC-16

- Đa dạng ăng-ten và điều khiển TX/RX / Bộ đệm khung TX/RX 128 Byte

- Bộ tổng hợp PLL với khoảng cách kênh 5 MHz và 500 kHz cho băng tần ISM 2.4 GHz

- Bảo mật phần cứng (AES, True Random Generator)

- Bộ tạo dao động tinh thể tích hợp (32.768 kHz & 16 MHz, cần có tinh thể bên ngoài)

- I/O và gói

- 33 Dòng I/O có thể lập trình

- QFN 48-pad (RoHS/Hoàn toàn xanh)

- Phạm vi nhiệt độ: -40°C đến 125°C Công nghiệp

- Tiêu thụ điện năng cực thấp (1.8 đến 3.6V) cho AVR & Rx/Tx: 10.1mA/18.6 mA

- Chế độ hoạt động của CPU (16 MHz): 4.1 mA

- Bộ thu phát 2.4GHz: RX_ON 6.0 mA / TX 14.5 mA (công suất đầu ra TX tối đa)

- Chế độ ngủ sâu: <700nA @ 25°C

- Cấp tốc độ: 0 – 16 MHz @ 1.8 – 3.6V phạm vi với vol tích hợptagcơ quan quản lý điện tử

Ứng dụng

- ZigBee®/ IEEE 802.15.4-2011/2006/2003™ – Thiết bị chức năng đầy đủ và giảm thiểu

- Bộ thu phát băng tần ISM 2.4 GHz mục đích chung với vi điều khiển

- RF4CE, SP100, WirelessHART™, Ứng dụng ISM và IPv6 / 6LoWPAN

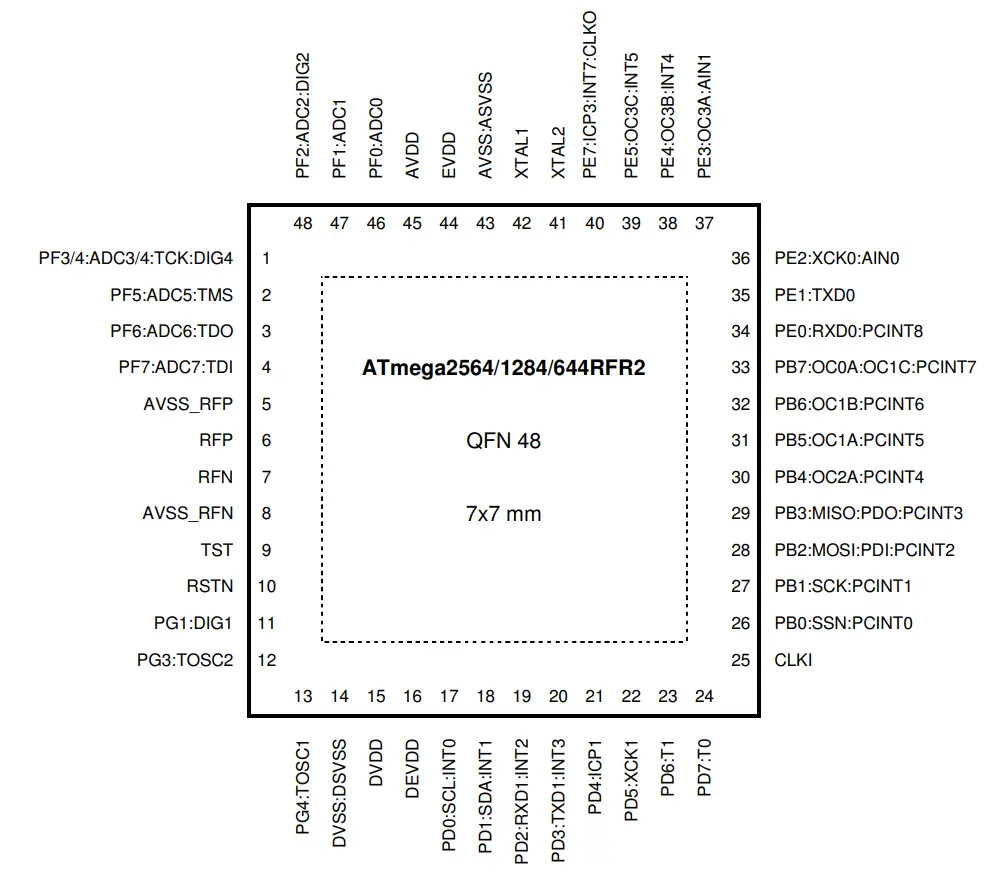

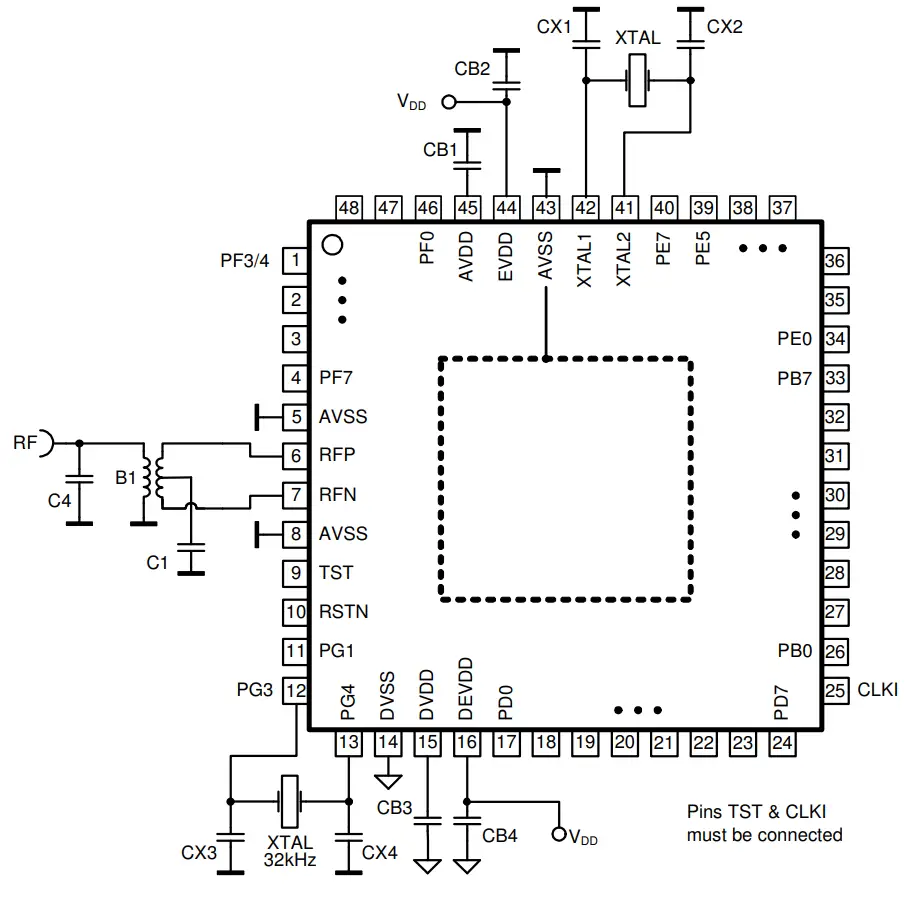

Cấu hình ghim

Hình 1-1. Sơ đồ chân ATmega2564/1284/644RFR2

Ghi chú: Miếng đệm trung tâm lớn bên dưới gói QFN/MLF được làm bằng kim loại và được kết nối bên trong với AVSS. Nó nên được hàn hoặc dán vào bảng để đảm bảo độ ổn định cơ học tốt. Nếu miếng đệm ở giữa không được kết nối, gói hàng có thể bị lỏng khỏi bo mạch. Không nên sử dụng mái chèo hở để thay thế cho các chân AVSS thông thường.

Tuyên bố miễn trừ trách nhiệm

Các giá trị điển hình có trong biểu dữ liệu này dựa trên kết quả mô phỏng và mô tả đặc tính của các bộ vi điều khiển AVR và bộ thu phát vô tuyến khác được sản xuất theo công nghệ xử lý tương tự. Giá trị tối thiểu và tối đa sẽ có sau khi thiết bị được mô tả.

Quaview

ATmega2564/1284/644RFR2 là bộ vi điều khiển CMOS 8 bit công suất thấp dựa trên kiến trúc RISC nâng cao AVR kết hợp với bộ thu phát tốc độ dữ liệu cao cho băng tần ISM 2.4 GHz.

Bằng cách thực hiện các lệnh mạnh mẽ trong một chu kỳ xung nhịp, thiết bị đạt được thông lượng gần 1 MIPS trên mỗi MHz, cho phép nhà thiết kế hệ thống tối ưu hóa mức tiêu thụ điện năng so với tốc độ xử lý.

Bộ thu phát vô tuyến cung cấp tốc độ dữ liệu cao từ 250 kb/s đến 2 Mb/s, xử lý khung, độ nhạy thu vượt trội và công suất phát đầu ra cao cho phép liên lạc không dây rất mạnh mẽ.

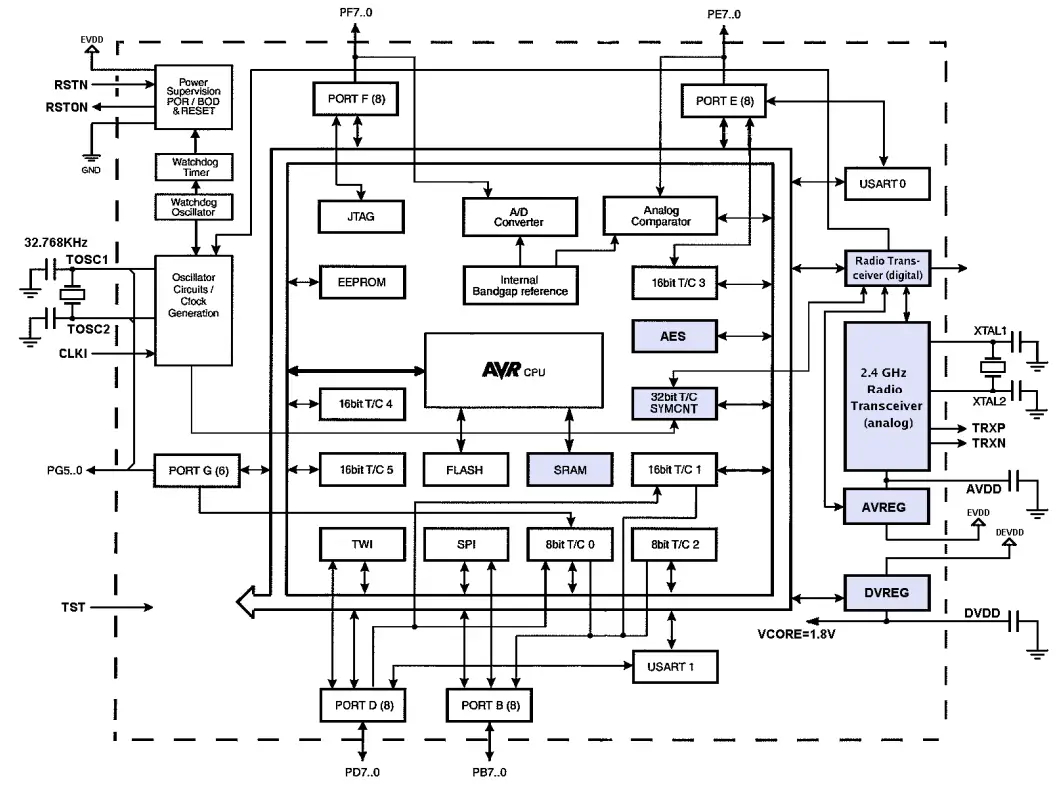

Sơ đồ khối

Hình 3-1 Sơ đồ khối

Lõi AVR kết hợp một tập lệnh phong phú với 32 thanh ghi làm việc cho mục đích chung. Tất cả 32 thanh ghi được kết nối trực tiếp với Đơn vị logic số học (ALU). Hai thanh ghi độc lập có thể được truy cập bằng một lệnh duy nhất được thực hiện trong một chu kỳ xung nhịp. Kiến trúc thu được rất hiệu quả về mã trong khi đạt được thông lượng nhanh hơn tới mười lần so với các bộ vi điều khiển CISC thông thường. Hệ thống bao gồm vol nội bộtagquy định điện tử và quản lý năng lượng tiên tiến. Được phân biệt bởi dòng điện rò rỉ nhỏ, nó cho phép kéo dài thời gian hoạt động của pin.

Bộ thu phát vô tuyến là giải pháp ZigBee tích hợp đầy đủ sử dụng số lượng thành phần bên ngoài tối thiểu. Nó kết hợp hiệu suất RF tuyệt vời với chi phí thấp, kích thước nhỏ và mức tiêu thụ dòng điện thấp. Bộ thu phát vô tuyến bao gồm bộ tổng hợp phân số N ổn định tinh thể, bộ phát và bộ thu, và xử lý tín hiệu phổ trải rộng chuỗi trực tiếp (DSSS) đầy đủ với việc trải rộng và giải trải rộng. Thiết bị hoàn toàn tương thích với các tiêu chuẩn IEEE802.15.4-2011/2006/2003 và ZigBee. ATmega2564/1284/644RFR2 cung cấp các tính năng sau: 256K/128K/64K Byte Flash có thể lập trình trong hệ thống (ISP) với khả năng đọc trong khi ghi, 8K/4K/2K Byte EEPROM, 32K/16K/8K Byte SRAM, tối đa 35 đường I/O mục đích chung, 32 thanh ghi làm việc mục đích chung, Bộ đếm thời gian thực (RTC), 6 Bộ đếm/Bộ hẹn giờ linh hoạt với chế độ so sánh và PWM, Bộ đếm/Bộ hẹn giờ 32 bit, 2 USART, Giao diện nối tiếp 2 dây theo định hướng byte, Bộ chuyển đổi tín hiệu tương tự sang tín hiệu số (ADC) 8 kênh, 10 bit với đầu vào vi sai tùy chọntage với mức tăng có thể lập trình, Bộ hẹn giờ giám sát có thể lập trình với Bộ dao động bên trong, cổng nối tiếp SPI, tuân thủ chuẩn IEEE 1149.1TAG Giao diện thử nghiệm, cũng được sử dụng để truy cập hệ thống gỡ lỗi trên chip và lập trình cùng 6 chế độ tiết kiệm điện có thể lựa chọn bằng phần mềm.

Chế độ Chờ dừng CPU trong khi vẫn cho phép SRAM, Bộ định thời/Bộ đếm, cổng SPI và hệ thống ngắt tiếp tục hoạt động. Chế độ Tắt nguồn lưu nội dung thanh ghi nhưng đóng băng Bộ tạo dao động, vô hiệu hóa tất cả các chức năng chip khác cho đến lần ngắt tiếp theo hoặc thiết lập lại phần cứng. Ở chế độ Tiết kiệm năng lượng, bộ hẹn giờ không đồng bộ tiếp tục chạy, cho phép người dùng duy trì cơ sở hẹn giờ trong khi phần còn lại của thiết bị đang ở chế độ ngủ. Chế độ Giảm nhiễu ADC dừng CPU và tất cả các mô-đun I/O ngoại trừ bộ định thời không đồng bộ và ADC, để giảm thiểu nhiễu chuyển mạch trong quá trình chuyển đổi ADC. Ở chế độ Chờ, bộ tạo dao động RC đang chạy trong khi phần còn lại của thiết bị đang ở chế độ ngủ. Điều này cho phép khởi động rất nhanh kết hợp với mức tiêu thụ điện năng thấp. Ở chế độ Chờ mở rộng, cả bộ tạo dao động RC chính và bộ định thời không đồng bộ đều tiếp tục chạy.

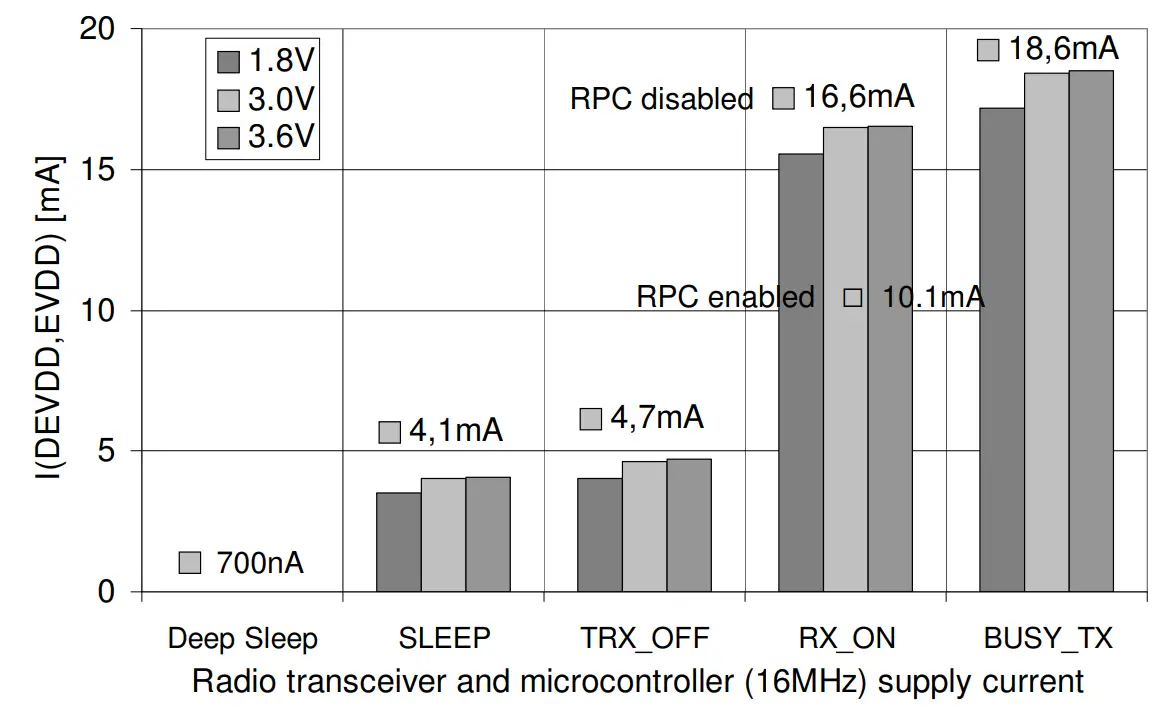

Dòng điện cung cấp điển hình của bộ vi điều khiển với xung nhịp CPU được đặt ở mức 16MHz và bộ thu phát vô tuyến cho các trạng thái quan trọng nhất được hiển thị trong Hình 3-2 bên dưới.

Hình 3-2 Dòng điện cung cấp của bộ thu phát vô tuyến và vi điều khiển (16MHz)

Công suất đầu ra truyền được đặt ở mức tối đa. Nếu bộ thu phát vô tuyến ở chế độ SLEEP thì dòng điện chỉ được tiêu tán bởi bộ vi điều khiển AVR.

Ở chế độ Ngủ sâu, tất cả các khối kỹ thuật số chính không có yêu cầu lưu giữ dữ liệu đều bị ngắt kết nối khỏi nguồn cung cấp dòng điện rò rỉ rất nhỏ. Bộ đếm thời gian cơ quan giám sát, bộ đếm ký hiệu MAC và bộ tạo dao động 32.768kHz có thể được cấu hình để tiếp tục chạy.

Thiết bị này được sản xuất bằng công nghệ bộ nhớ không mất dữ liệu mật độ cao của Atmel.

ISP Flash trên chip cho phép bộ nhớ chương trình được lập trình lại trong hệ thống thông qua giao diện nối tiếp SPI, bởi một lập trình viên bộ nhớ không biến đổi thông thường hoặc bằng chương trình khởi động trên chip chạy trên lõi AVR. Chương trình khởi động có thể sử dụng bất kỳ giao diện nào để tải xuống chương trình ứng dụng trong bộ nhớ Flash của ứng dụng.

Phần mềm trong phần Flash khởi động sẽ tiếp tục chạy trong khi phần Flash ứng dụng được cập nhật, cung cấp thao tác Đọc-Trong khi-Ghi thực sự. Bằng cách kết hợp CPU RISC 8 bit với Flash tự lập trình trong hệ thống trên chip nguyên khối, Atmel ATmega2564/1284/644RFR2 là bộ vi điều khiển mạnh mẽ cung cấp giải pháp rất linh hoạt và tiết kiệm chi phí cho nhiều ứng dụng điều khiển nhúng.

ATmega2564/1284/644RFR2 AVR được hỗ trợ bởi bộ công cụ phát triển hệ thống và chương trình đầy đủ bao gồm: trình biên dịch C, trình biên dịch macro, trình gỡ lỗi/mô phỏng chương trình, trình mô phỏng trong mạch và bộ công cụ đánh giá.

Mô tả Pin

EVDD

Nguồn cung cấp analog bên ngoàitage.

DEVDD

Nguồn cung cấp kỹ thuật số bên ngoài voltage.

AVDD

Nguồn cung cấp analog được quy địnhtage (được tạo ra bên trong).

DVDD

Lượng cung cấp kỹ thuật số được điều chỉnhtage (được tạo ra bên trong).

ĐVSS

Mặt đất kỹ thuật số.

AVSS

Mặt đất tương tự.

Cổng B (PB7…PB0)

Cổng B là cổng I/O hai chiều 8 bit có điện trở kéo lên bên trong (được chọn cho mỗi bit). Bộ đệm đầu ra của Cổng B có đặc tính truyền động đối xứng với cả khả năng thu và nguồn cao. Là đầu vào, các chân của Cổng B được kéo xuống mức thấp bên ngoài sẽ cung cấp dòng điện nếu điện trở kéo lên được kích hoạt. Các chân của Cổng B có ba trạng thái khi điều kiện reset được kích hoạt, ngay cả khi đồng hồ không chạy.

Cổng B cũng cung cấp các chức năng của nhiều tính năng đặc biệt khác nhau của ATmega2564/1284/644RFR2.

Cổng D (PD7…PD0)

Cổng D là cổng I/O hai chiều 8 bit với điện trở kéo lên bên trong (được chọn cho từng bit). Bộ đệm đầu ra của Cổng D có đặc tính truyền động đối xứng với cả khả năng chìm và nguồn cao. Là đầu vào, các chân Cổng D được kéo xuống thấp bên ngoài sẽ cấp nguồn dòng điện nếu điện trở kéo lên được kích hoạt. Các chân Cổng D được ba trạng thái khi điều kiện đặt lại trở nên hoạt động, ngay cả khi xung nhịp không chạy.

Cổng D cũng cung cấp các chức năng của nhiều tính năng đặc biệt khác nhau của ATmega2564/1284/644RFR2.

Cổng E (PE7,PE5…PE0)

Bên trong Port E là cổng I/O hai chiều 8 bit với điện trở kéo lên bên trong (được chọn cho từng bit). Bộ đệm đầu ra Port E có đặc tính truyền động đối xứng với cả khả năng sink và source cao. Là đầu vào, các chân Port E được kéo xuống thấp bên ngoài sẽ cung cấp dòng điện nếu điện trở kéo lên được kích hoạt. Các chân Port E được đặt ở trạng thái ba khi điều kiện reset trở nên hoạt động, ngay cả khi xung nhịp không chạy.

Do số lượng chân thấp của gói QFN48 nên cổng E6 không được kết nối với chân. Cổng E cũng cung cấp các chức năng của nhiều tính năng đặc biệt khác nhau của ATmega2564/1284/644RFR2.

Port F (PF7..PF5,PF4/3,PF2…PF0)

Cổng F bên trong là cổng I/O hai chiều 8 bit có điện trở kéo lên bên trong (được chọn cho mỗi bit). Bộ đệm đầu ra của Cổng F có đặc tính truyền động đối xứng với cả khả năng thu và nguồn cao. Là đầu vào, các chân của Port F được kéo xuống mức thấp bên ngoài sẽ cung cấp dòng điện nếu điện trở kéo lên được kích hoạt. Các chân của Port F có ba trạng thái khi điều kiện reset được kích hoạt, ngay cả khi đồng hồ không chạy.

Do số lượng chân thấp của gói QFN48 nên cổng F3 và F4 được kết nối với cùng một chân. Cấu hình I/O phải được thực hiện cẩn thận để tránh tiêu hao điện năng quá mức.

Cổng F cũng cung cấp các chức năng của nhiều tính năng đặc biệt khác nhau của ATmega2564/1284/644RFR2.

Cổng G (PG4,PG3,PG1)

Cổng G bên trong là cổng I/O hai chiều 6 bit có điện trở kéo lên bên trong (được chọn cho mỗi bit). Bộ đệm đầu ra của Cổng G có đặc tính truyền động đối xứng với cả khả năng thu và nguồn cao. Tuy nhiên cường độ driver của PG3 và PG4 bị giảm so với các chân cổng khác. Khối lượng đầu ratage drop (VOH, VOL) cao hơn trong khi dòng rò rỉ nhỏ hơn. Là đầu vào, các chân Port G được kéo xuống thấp bên ngoài sẽ cung cấp dòng điện nếu điện trở kéo lên được kích hoạt. Các chân Port G được ba trạng thái khi điều kiện đặt lại trở nên hoạt động, ngay cả khi đồng hồ không chạy.

Do số lượng chân thấp của cổng gói QFN48 G0, G2 và G5 không được kết nối với chân.

Cổng G cũng cung cấp các chức năng của nhiều tính năng đặc biệt khác nhau của ATmega2564/1284/644RFR2.

Yêu cầu báo giá AVSS

AVSS_RFP là một chân nối đất chuyên dụng cho cổng I/O RF vi sai hai chiều.

AVSS_RFN

AVSS_RFN là chân nối đất chuyên dụng cho cổng I/O RF vi sai hai chiều.

Yêu cầu đề xuất

RFP là cực dương của cổng I/O RF vi sai, hai chiều.

RFN

RFN là cực âm của cổng I/O RF vi sai hai chiều.

RSTN

Đặt lại đầu vào. Mức thấp trên chân này lâu hơn độ dài xung tối thiểu sẽ tạo ra tín hiệu reset, ngay cả khi đồng hồ không chạy. Các xung ngắn hơn không được đảm bảo để tạo ra thiết lập lại.

XTAL1

Đầu vào bộ dao động tinh thể đảo ngược 16 MHz amplifier. Nói chung, một tinh thể giữa XTAL1 và XTAL2 cung cấp xung nhịp tham chiếu 16 MHz của bộ thu phát vô tuyến.

XTAL2

Đầu ra của bộ dao động tinh thể đảo ngược 16 MHz ampchất lót.

Tst

Chế độ lập trình và kiểm tra kích hoạt pin. Nếu chân TST không được sử dụng, hãy kéo nó xuống mức thấp.

CLKI

Đầu vào cho hệ thống đồng hồ. Nếu được chọn, nó sẽ cung cấp đồng hồ hoạt động của bộ vi điều khiển.

Pin chưa sử dụng

Chân nổi có thể gây tiêu tán điện năng ở đầu vào kỹ thuật sốtage. Chúng phải được kết nối với một nguồn thích hợp. Trong chế độ hoạt động bình thường, điện trở kéo lên bên trong có thể được bật (trong Reset, tất cả GPIO được cấu hình là đầu vào và điện trở kéo lên vẫn chưa được bật).

Các chân I/O hai chiều không được kết nối trực tiếp với đất hoặc nguồn điện.

Các chân đầu vào kỹ thuật số TST và CLKI phải được kết nối. Nếu chân TST không sử dụng có thể được kết nối với AVSS trong khi CLKI phải được kết nối với DVSS.

Các chân đầu ra được điều khiển bởi thiết bị và không nổi. Các chân cấp nguồn tương ứng được kết nối với nhau bên trong.

XTAL1 và XTAL2 sẽ không bao giờ bị buộc phải cung cấp voltagvà cùng một lúc.

Khả năng tương thích và giới hạn tính năng của gói QFN-48

AREF

Tập tham khảotagĐầu ra của bộ chuyển đổi A/D không được kết nối với chân trong ATmega2564/1284/644RFR2.

Cổng E6

Cổng E6 không được kết nối với chân trong ATmega2564/1284/644RFR2. Chân thay thế có chức năng là đầu vào xung nhịp cho bộ hẹn giờ 3 và ngắt ngoài 6 không khả dụng.

Cổng F3 và F4

Cổng F3 và F4 được kết nối với cùng một chân trong ATmega2564/1284/644RFR2. Cấu hình đầu ra phải được thực hiện cẩn thận để tránh tiêu thụ dòng điện quá mức.

Chức năng chân thay thế của cổng F4 được sử dụng bởi JTAG giao diện. Nếu JTAG giao diện được sử dụng, cổng F3 phải được cấu hình làm đầu vào và chức năng chân thay thế đầu ra DIG4 (chỉ báo RX/TX) phải bị vô hiệu hóa. Nếu không, JTAG giao diện sẽ không hoạt động. Cầu chì SPIEN phải được lập trình để có thể xóa chương trình vô tình điều khiển cổng F3.

Chỉ có 7 kênh đầu vào một đầu cho ADC có sẵn.

Cổng G0

Cổng G0 không được kết nối với chân trong ATmega2564/1284/644RFR2. Chức năng chân thay thế DIG3 (chỉ báo RX/TX đảo ngược) không khả dụng. Nếu JTAG Giao diện không được sử dụng, chức năng chân thay thế DIG4 đầu ra của cổng F3 vẫn có thể được sử dụng làm chỉ báo RX/TX.

Cổng G2

Cổng G2 không được kết nối với chân trong ATmega2564/1284/644RFR2. Chức năng chân thay thế AMR (đầu vào đọc đồng hồ tự động không đồng bộ cho bộ đếm thời gian 2) không khả dụng.

Cổng G5

Cổng G5 không được kết nối với chân trong ATmega2564/1284/644RFR2. Chức năng chân thay thế OC0B (kênh so sánh đầu ra của bộ định thời 8 bit 0) không khả dụng.

RSTON

Đầu ra đặt lại RSTON báo hiệu trạng thái đặt lại bên trong không được kết nối với chân trong ATmega2564/1284/644RFR2.

Tóm tắt cấu hình

Tùy theo yêu cầu của ứng dụng, kích thước bộ nhớ có thể thay đổi cho phép tối ưu hóa mức tiêu thụ dòng điện và dòng rò.

Bảng 3-1 Cấu hình bộ nhớ

| Thiết bị | Đèn nháy | Bộ nhớ EEPROM | SRAM |

| ATmega2564RFR2 | 256KB | 8KB | 32KB |

| ATmega1284RFR2 | 128KB | 4KB | 16KB |

| ATmega644RFR2 | 64KB | 2KB | 8KB |

Cấu hình gói và mã pin liên quan giống nhau đối với tất cả các thiết bị cung cấp đầy đủ chức năng cho ứng dụng.

Bảng 3-2 Cấu hình hệ thống

| Thiết bị | Bưu kiện | GPIO | NẾU nối tiếp | kênh ADC |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

Các thiết bị được tối ưu hóa cho các ứng dụng dựa trên đặc điểm kỹ thuật ZigBee và IEEE 802.15.4. Có thể có ngăn xếp ứng dụng, lớp mạng, giao diện cảm biến và bộ điều khiển năng lượng tuyệt vời được kết hợp trong một con chip duy nhất và có thể hoạt động trong nhiều năm.

Bảng 3-3 Ứng dụng Profile

| Thiết bị | Ứng dụng |

| ATmega2564RFR2 | Bộ điều phối / Bộ định tuyến mạng lớn cho IEEE 802.15.4 / ZigBee Pro |

| ATmega1284RFR2 | Bộ điều phối mạng / Bộ định tuyến cho IEEE 802.15.4 |

| ATmega644RFR2 | Thiết bị nút cuối/bộ xử lý mạng |

Mạch ứng dụng

Sơ đồ ứng dụng cơ bản

Sơ đồ ứng dụng cơ bản của ATmega2564/1284/644RFR2 với đầu nối RF một đầu được thể hiện trong Hình 4-1 bên dưới và Bảng vật liệu liên quan trong Bảng 4-1 ở trang 10. Đầu vào RF một đầu 50Ω được chuyển đổi thành trở kháng cổng RF vi sai 100Ω bằng Balun B1. Tụ điện C1 và C2 cung cấp ghép nối AC của đầu vào RF với cổng RF, tụ điện C4 cải thiện khả năng khớp nối.

Hình 4-1. Sơ đồ ứng dụng cơ bản (gói 48 chân)

Tụ điện bypass nguồn điện (CB2, CB4) được kết nối với chân cung cấp analog bên ngoài (EVDD, chân 44) và chân cung cấp kỹ thuật số bên ngoài (DEVDD, chân 16). Tụ điện C1 cung cấp sự ghép nối AC cần thiết của RFN/RFP.

Các chân nổi có thể gây ra sự tiêu hao điện năng quá mức (ví dụ khi bật nguồn). Chúng phải được kết nối với nguồn thích hợp. GPIO không được kết nối trực tiếp với đất hoặc nguồn điện.

Các chân đầu vào kỹ thuật số TST và CLKI phải được kết nối. Nếu chân TST không bao giờ được sử dụng thì nó có thể được kết nối với AVSS trong khi chân CLKI không sử dụng có thể được kết nối với DVSS (xem chương “Các chân không được sử dụng”).

Tụ điện CB1 và CB3 là tụ điện bypass cho khối lượng kỹ thuật số và tương tự tích hợptagBộ điều chỉnh để đảm bảo hoạt động ổn định và cải thiện khả năng chống ồn.

Các tụ điện nên được đặt càng gần các chân càng tốt và phải có điện trở thấp cũng như độ tự cảm thấp kết nối với mặt đất để đạt được hiệu suất tốt nhất.

Tinh thể (XTAL), hai tụ điện tải (CX1, CX2) và mạch điện bên trong được kết nối với các chân XTAL1 và XTAL2 tạo thành bộ dao động tinh thể 16MHz cho bộ thu phát 2.4GHz. Để đạt được độ chính xác và độ ổn định tốt nhất của tần số tham chiếu, phải tránh các điện dung ký sinh lớn. Các đường tinh thể phải được định tuyến càng ngắn càng tốt và không ở gần các tín hiệu I/O kỹ thuật số. Điều này đặc biệt cần thiết đối với các Chế độ Tốc độ Dữ liệu Cao.

Tinh thể 32.768 kHz được kết nối với bộ tạo dao động tinh thể công suất thấp (phụ 1µA) bên trong cung cấp tham chiếu thời gian ổn định cho tất cả các chế độ năng lượng thấp bao gồm Bộ đếm biểu tượng 32 bit IEEE 802.15.4 (“Bộ đếm biểu tượng MAC”) và ứng dụng đồng hồ thời gian thực sử dụng không đồng bộ bộ đếm thời gian T/C2 (“Bộ đếm thời gian/Bộ đếm 2 với chế độ hoạt động không đồng bộ và điều khiển bằng xung điện”).

Tổng điện dung shunt bao gồm CX3, CX4 không được vượt quá 15pF trên cả hai chân.

Dòng điện cung cấp rất thấp của bộ dao động đòi hỏi phải bố trí PCB cẩn thận và phải tránh mọi đường rò rỉ.

Nhiễu xuyên âm và bức xạ từ việc chuyển tín hiệu số sang chân thạch anh hoặc chân RF có thể làm giảm hiệu suất hệ thống. Nên lập trình cài đặt cường độ ổ đĩa tối thiểu cho tín hiệu đầu ra kỹ thuật số (xem “DPDS0 – Thanh ghi cường độ trình điều khiển cổng 0”).

Bảng 4-1. Danh mục vật liệu (BoM)

| Người thiết kế | Sự miêu tả | Giá trị | Nhà sản xuất | Mã số sản phẩm | Bình luận |

| B1 | balun SMD

Balun/bộ lọc SMD |

2.4 GHz | Công nghệ Wuerth Johanson | 748421245

2450FB15L0001 |

Bao gồm bộ lọc |

| CB1 CB3 | LDO VREG

tụ điện bỏ qua |

1 mF (tối thiểu 100nF) | AVX

Murata |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10% 16V |

| CB2 CB4 | Tụ điện bypass nguồn điện | 1 mF (tối thiểu 100nF) | |||

| CX1, CX2 | Tụ tải tinh thể 16 MHz | 12pF | AVX

Murata |

06035A120JA GRP1886C1H120JA01 | RĂNG CƯA (0603) 5% 50V |

| CX3, CX4 | Tụ tải tinh thể 32.768kHz | 12… 25 pF | |||

| C1, C2 | Tụ ghép RF | 22pF | Epcos Epcos AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50V (0402 hoặc 0603) |

| C4 (tùy chọn) | Khớp RF | 0.47pF | Công ty TNHH Johnstech | ||

| XTAL | Pha lê | CX-4025 16 MHz

SX-4025 16 MHz |

ACAL Taitjen Siward | XWBBPL-F-1 A207-011 | |

| XTAL 32kHz | Pha lê | R = 100 kOhm |

Lịch sử sửa đổi

Xin lưu ý rằng số trang giới thiệu trong phần này đang đề cập đến tài liệu này. Bản sửa đổi tham chiếu trong phần này đang đề cập đến bản sửa đổi tài liệu.

Rev. 42073BS-MCU Wireless-09/14

- Nội dung không thay đổi – được tạo lại để phát hành kết hợp với bảng dữ liệu.

Rev. 8393AS-MCU Wireless-02/13

- Phiên bản phát hành đầu tiên.

© 2014 Atmel Corporation. Bảo lưu mọi quyền. / Rev.: 42073BS-MCU Wireless-09/14 Atmel®, logo Atmel và các kết hợp của chúng, Enabling Unlimited Possibilities® và các nhãn hiệu khác là nhãn hiệu đã đăng ký hoặc nhãn hiệu của Atmel Corporation hoặc các công ty con của Atmel Corporation. Các thuật ngữ và tên sản phẩm khác có thể là nhãn hiệu của những người khác.

Tuyên bố miễn trừ trách nhiệm: Thông tin trong tài liệu này được cung cấp liên quan đến các sản phẩm của Atmel. Không có giấy phép nào, rõ ràng hay ngụ ý, bằng biện pháp cấm vận hay cách khác, đối với bất kỳ quyền sở hữu trí tuệ nào được cấp theo tài liệu này hoặc liên quan đến việc bán các sản phẩm của Atmel. NGOẠI TRỪ NHƯ ĐƯỢC QUY ĐỊNH TRONG CÁC ĐIỀU KHOẢN VÀ ĐIỀU KIỆN BÁN HÀNG CỦA ATMEL TRÊN ATMEL WEBSITE, ATMEL ASSUMES KHÔNG CHỊU TRÁCH NHIỆM PHÁP LÝ NÀO VÀ TUYÊN BỐ TỪ CHỐI BẤT KỲ BẢO ĐẢM RÕ RÀNG, NGỤ Ý HOẶC TRUYỆN NGHĨA LIÊN QUAN ĐẾN CÁC SẢN PHẨM CỦA NÓ BAO GỒM, NHƯNG KHÔNG GIỚI HẠN ĐỐI VỚI BẢO ĐẢM NGẪU NHIÊN VỀ KHẢ NĂNG MẠNH MẼ HOẶC PHÙ HỢP CHO MỘT MỤC ĐÍCH. TRONG MỌI TRƯỜNG HỢP, ATMEL SẼ CHỊU TRÁCH NHIỆM PHÁP LÝ ĐỐI VỚI BẤT KỲ THIỆT HẠI TRỰC TIẾP, CHỈ ĐỊNH, HẬU QUẢ, CÁ NHÂN, ĐẶC BIỆT HOẶC BẤT CỨ SỰ CỐ (BAO GỒM, KHÔNG GIỚI HẠN, THIỆT HẠI DO MẤT VÀ LỢI NHUẬN, LỢI NHUẬN DOANH NGHIỆP, HOẶC MẤT THÔNG TIN) PHÁT SINH NGOÀI VIỆC SỬ DỤNG HOẶC BẤT HỢP PHÁP TÀI LIỆU NÀY, NGAY CẢ NẾU ATMEL ĐÃ ĐƯỢC TƯ VẤN VỀ KHẢ NĂNG CỦA CÁC THIỆT HẠI NHƯ VẬY. Atmel không tuyên bố hoặc bảo đảm về tính chính xác hoặc đầy đủ của nội dung tài liệu này và có quyền thay đổi thông số kỹ thuật và mô tả sản phẩm bất kỳ lúc nào mà không cần thông báo. Atmel không đưa ra bất kỳ cam kết nào về việc cập nhật thông tin có trong tài liệu này. Trừ khi có quy định cụ thể khác, các sản phẩm Atmel không phù hợp và sẽ không được sử dụng trong các ứng dụng ô tô. Các sản phẩm của Atmel không nhằm mục đích, ủy quyền hoặc bảo hành để sử dụng làm thành phần trong các ứng dụng nhằm hỗ trợ hoặc duy trì sự sống.

Thiết bị điện tử Mouser

Nhà phân phối được ủy quyền

Nhấp để View Thông tin về giá cả, hàng tồn kho, giao hàng & vòng đời:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

Hỗ trợ khách hàng

Tập đoàn Atmel

Ổ đĩa công nghệ 1600

San Jose, CA 95110

Hoa Kỳ

Điện thoại: (+1)408-441-0311

Fax: (+1)408-487-2600

www.atmel.com

Tài liệu / Tài nguyên

|

Vi điều khiển AVR Atmel ATmega2564 8bit [tập tin pdf] Hướng dẫn sử dụng ATmega2564RFR2, ATmega1284RFR2, ATmega644RFR2, ATmega2564 Vi điều khiển AVR 8bit, ATmega2564, Vi điều khiển AVR 8bit, Vi điều khiển AVR, Vi điều khiển |